# Beat 주파수 성분을 이용한 Two Stage 인버터의 DC-Link 커페시터 상태 모니터링 기법

고예은, 남은택, 채수용 포항공과대학교

# DC-Link Capacitor Condition Monitoring Method of Two Stage Inverter using Beat Frequency Components

Yeeun Ko, Euntaek Nam, Suyong Chae Pohang University of Science and Technology

#### **ABSTRACT**

본 논문은 Two stage 인버터의 6차 고조파 성분과 스위청 주파수 차이로 생성되는 Beat 주파수(Beat Frequency) 성분을 이용하여 DC-Link 커패시터의 커패시턴스와 ESR(Equivalent Series Resistance)을 추정하는 방법을 제시한다. 제안된 방식은 시스템 고유의 고조파를 활용하고 비트 주파수를 자유롭게 생성하여 추정하는 비침습적 방식이며, 이를 통해 DC-Link 커패시터의 파라미터를 실시간으로 추정할 수 있다. 추정의 정확도를 향상시키기 위하여 커패시턴스 성분이 주로 나타나는 6차고조파 주파수에서 커패시턴스를 추정하고, ESR 성분이 주로 나타나는 주파수 영역의 Beat 주파수를 생성하여 ESR을 추정한다. 제안된 알고리즘은 10kW급 3상 Two stage 인버터를 대상으로 MATLAB/Simulink 시뮬레이션을 통하여 검증하였다.

#### 1. 서 론

재생에너지 및 에너지저장시스템과 같은 분산 자원이 전력계통에 효과적으로 연결되기 위해서는 계통연계 인버터가 필요하며, 전압 변동을 최소화하고 고조파를 완화하기 위하여 인버터 내 DC-Link 커패시터는 필수적으로 사용된다. 그러나 커패시터는 다른 구성요소에 비해 열 충격 및 노화에 취약하여 시스템의 신뢰성에 큰 영향을 미친다. 실제로 커패시터 성능 저하는 컨버터 결함의 약 30%를 차지하는 주요 원인으로, 신뢰할 수 있는 운전 및 예방적 유지보수를 보장하기 위해 작동 중커패시터의 상태를 모니터링하는 연구가 활발히 진행되고 있다.[11][2][3]

커패시터 상태 모니터링의 지표로는 주로 커패시턴스와 ESR이 사용되며, 두 파라미터의 추정을 통해 커패시터의 초기성능 대비 성능 저하를 정량적으로 판단할 수 있다. 전해 커패시터의 경우에는 초기값 대비 커패시턴스가 20% 감소하거나 ESR이 2.8배 증가하면 커패시터의 수명이 종료된 것으로 간주한다.[2]

커패시터 매개변수를 추정하는 기존의 방법은 주기적인 소신호 리플 기반 원리, 비주기적인 대신호 충/방전 프로파일 기반 원리, 커패시터 모델을 고려하지 않고 데이터 학습 알고리 즘을 사용하는 블랙박스 모델 기반 원리 등으로 분류된다. 계통연계 인버터의 DC-Link 커패시턴스 및 ESR 추정은 주로 소신호 리플 기반 원리를 사용하며 이 경우, 스위칭 주파수 리플 성분의 분석을 위해 빠른 샘플링 속도에 기반한 데이터 취득

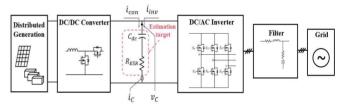

그림 1 Two stage 인버터 시스템 구성

Fig. 1 Configuration of the Two stage Inverter System

득이 필요한 단점이 있다. 본 논문에서는 스위칭 리플보다 현저히 낮은 주파수인 Beat 주파수와 6차 고조파를 활용해 샘플링 속도 요구사항을 낮춘다. 일반적으로 Two stage 인버터에서 적용되는 대용량 DC-Link 커패시터는 6차 고조파 주파수영역에서 커패시턴스 성분이 주로 나타난다. Beat 주파수는 ESR 성분이 주로 나타나는 주파수로 생성하여 커패시턴스는 6차 고조파에서, ESR은 Beat 주파수에서 추정한다. 이와 같이커패시턴스와 ESR 성분이 두드러지는 두 주파수에서 파라미터를 추정함으로써 추정 정확성을 향상시킨다.

#### 2. 본 론

#### 2.1 Beat 주파수

본 논문은 Two stage 인버터의 6차 고조파와 Beat 주파수성분을 이용해 DC-Link 커패시터의 커패시턴스와 ESR을 실시간으로 추정하는 기법을 제안한다. 그림 1과 같이 DC-link 커패시터의 커패시턴스는  $C_{dc}$ 로, ESR은  $R_{ESR}$ 로 표현한다. 추정에 사용되는 6차 고조파는 시스템 작동 중에 본질적으로 생성되는 성분이며, Beat 주파수는 서로 다른 주파수를 가진 두신호가 중첩되었을 때 발생하는 간섭 현상에 의해 생성된다.

본 논문에서는 부스트 컨버터와 Two stage 인버터 간의 스위칭 주파수를 조절하여 두 스위칭 주파수 차이에 해당하는 Beat 주파수 성분을 생성하여 커패시터 상태 추정에 활용한다.

Beat 주파수 생성 과정은 다음과 같다. 그림 1의  $i_{con}$ 와  $i_{inv}$ 는 각각 컨버터 측 리플 전류와 Two stage 인버터 측 리플 전류를 나타내며, 두 리플 전류의 진폭을 각각  $i_a$ 과  $i_b$ 로 표현한다. 컨버터의 스위칭 주파수와 Two stage 인버터의 스위칭 주파수를  $f_a$ 과  $f_b$ 로 표현하고 각주파수는  $w_a$ 과  $w_b$ 로 표현한다.

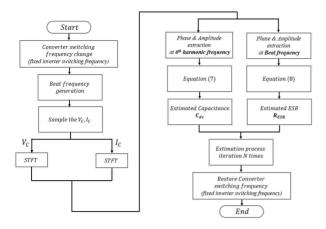

그림 2 제안 알고리즘 블록 다이어그램 Fig. 2 Block Diagram of Proposed Algorithm

컨버터 측 리플 전류와 Two stage 인버터 측의 리플 전류를 기본 고조파로 근사하면 식 (1)과 같이 나타낼 수 있다.

$$\begin{cases} i_{con} \simeq i_a \cos(2\pi f_a t) = i_a \cos(w_a t) \\ i_{inv} \simeq i_b \cos(2\pi f_b t) = i_b \cos(w_b t) \end{cases}$$

(1)

DC-Link에는 두 전류의 차에 해당하는 전류  $i_c$ 가 흐르며, 이는 식 (2)로 표현할 수 있다.

$$\begin{split} i_{C} &= i_{con} - i_{i_{nv}} \\ &= i_{a} \mathrm{cos}(\frac{w_{a} + w_{b}}{2}t + \frac{w_{a} - w_{b}}{2}t) + i_{b} \mathrm{cos}(\frac{w_{a} + w_{b}}{2}t - \frac{w_{a} - w_{b}}{2}t) \\ &= (i_{a} + i_{b}) \mathrm{cos}(\frac{w_{a} + w_{b}}{2}t) \mathrm{cos}(\frac{w_{a} - w_{b}}{2}t) \\ &- (i_{a} - i_{b}) \mathrm{sin}(\frac{w_{a} + w_{b}}{2}t) \mathrm{sin}(\frac{w_{a} - w_{b}}{2}t) \end{split}$$

DC-Link 전류는 두 스위칭 주파수의 평균값에 해당하는 리플을 포함하고 있으며 스위칭 주파수 차의 평균에 해당하는 주파수는 상대적으로 매우 낮아 진폭의 변화로 인식된다. 이 함수의 진폭이 최소화되는 주파수는 스위칭 주파수 차의 두 배로식 (3)과 같이 표현되며, 이는 DC-Link 전류 및 전압에서 관찰되는 Beat 주파수  $f_{beat}$ 를 나타낸다.

$$f_{beat} = |f_a - f_b| \tag{3}$$

# 2.2 커패시터 파라미터 추정 알고리즘

Two stage 인버터 시스템의 기본 동작 중 DC-Link 커패시터의 상태 추정이 필요할 때, 인버터의 스위칭 주파수는 고정하고 컨버터의 스위칭 주파수를 가변하여 원하는 Beat 주파수성분을 생성한다. 이후 추정 알고리즘을 적용한 후 스위칭 주파수를 원래대로 복구하여 시스템을 다음 추정 구간 전까지 기존 동작 조건으로 운영한다. 그림 2와 같이 과정을 반복해 시스템을 중단하지 않고 실시간으로 커패시턴스 및 ESR을 추정할 수 있다.

DC-Link 커패시터의 전압 및 전류에서 관찰되는 6차 고조

파와 Beat 주파수 성분을 활용하여 커페시턴스 및 ESR을 추정하기 위해서는 시간 영역의 신호를 주파수 영역으로 변환하는 과정이 필수적이며, 이는 주파수 분석 기법 중 하나인 STFT(Short-Time Fourier Transform)를 통해 효과적으로 수행될 수 있다.

$$X[n,k] = \sum_{m=n-(N_{n}-1)}^{n} w[n-mR]x[m]e^{-jw_{k}m}$$

(4)

STFT는 식 (4)로 표현되며, x는 분석 대상 신호, w는 윈도우 함수, n과 k는 각각 시간 및 주파수 인덱스, R은 오버랩을 나타낸다. DC-Link 커패시터의 전압 및 전류를 STFT 처리하면 신호 내 포함된 주파수의 인덱스에 해당하는 진폭과 위상 정보를 얻을 수 있다. 이를 활용하여 DC-Link 커패시터의 전압 및 전류 신호에서 6차 고조파 주파수 및 Beat 주파수의 진폭과 위상 정보를 추출하고 커패시턴스 및 ESR 계산 과정을 거친다.

$$Z = R_{ESR} + \frac{1}{j2\pi f C_{dc}} \tag{5}$$

$$|Z| \angle \alpha^{\circ} = \frac{|V_C| \angle \theta_V^{\circ}}{|I_C| \angle \theta_I^{\circ}}$$

(6)

$$C_{dc} = \frac{1}{2\pi f_{6^{th}} R_{ESR} \tan(\alpha_{6^{th}}^{\circ})}$$

(7)

$$R_{ESR} = \sqrt{\frac{\left|Z_{f_b}\right|^2}{1 + \tan(\alpha_{boat}^{\circ})^2}} \tag{8}$$

Z는 DC-Link 커페시터의 임피던스,  $\alpha_{g^{th}}$ ,  $\alpha_{beat}$ 는 6차 고조파 주파수 및 Beat 주파수에서의 임피던스의 위상,  $\theta_V$ ,  $\theta_I$ 는 커페시터 전압의 위상과 전류의 위상,  $\left|Z_{f_b}\right|$ 는 Beat 주파수에서의 임피던스 크기를 의미한다. DC-Link 커페시터의 임피던스는 식 (5)로 표현되며, 페이저 형태로는 식 (6)과 같이 나타낼 수 있다.

STFT 과정 후 추출한 전압 및 전류의 6차 고조파 주파수 성분 위상을 통하여 식 (7)의  $\alpha_{6^{th}}$ 을 계산할 수 있고, Beat 주파수 성분 진폭 및 위상을 통하여 식 (8)의  $\left|Z_{f_b}\right|$ 와  $\alpha_{beat}$ 를 계산할 수 있다.

본 논문에서 다루는 Two stage 인버터 시스템의 6차 고조파 주파수는 360Hz로 커패시터의 임피던스에서 커패시턴스 성분이 주로 나타나는 영역에 속한다. 따라서, 6차 고조파 주파수에서 식 (7)을 통해 커패시턴스를 계산하고 ESR 성분이 주로나타나는 Beat 주파수에서 식 (8)로 ESR을 계산하여 추정의정확성을 향상시킨다.

## 2.3 시뮬레이션 결과

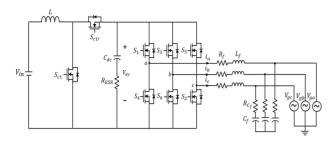

제안된 추정 기법은 MATLAB/Simulink 시뮬레이션을 통해 10kW급 3상 Two stage 인버터를 대상으로 검증되었으며, 그림 3의 시스템 파라미터는 표 1과 같다. 컨버터와 인버터의 스위칭 주파수는 각각 18kHz와 15kHz로 설정하여 3kHz의 Beat 주파수를 생성한다. 알고리즘 검증을 위하여 시간에 따라 노화되는 DC-Link 커페시터를 표 2와 같이 모의하며 초기값 대비

그림 3 3상 Two stage 인버터 시스템

Fig. 3 Three-Phase Two stage Inverter System

표 1 Two stage 인버터 시스템 파라미터 Table 1 Parameters of Two stage Inverter System

| Parameter | Value   | Parameter | Value    |

|-----------|---------|-----------|----------|

| Duty      | 0.5     | $V_{in}$  | 350 [V]  |

| $V_{dc}$  | 700 [V] | L         | 4.3 [mH] |

| $R_f$     | 0.1 [Ω] | $L_f$     | 2 [mH]   |

| $V_g$     | 380 [V] | $C_f$     | 25 [μF]  |

표 2 DC-Link 커패시터 파라미터 Table 2 Parameters of DC-Link Capacitor

| Parameter | Case (1) | Case (2)     | Case (3) |

|-----------|----------|--------------|----------|

| $C_{dc}$  | 3 [mF]   | $2.8 \ [mF]$ | 2.4 [mF] |

| $R_{ESR}$ | 0.05 [Ω] | 0.1 [Ω]      | 0.14 [Ω] |

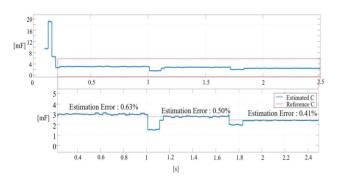

그림 4 DC-Link 커패시터의 커패시턴스 추정 결과 Fig. 4 DC-Link Capacitor Capacitance Estimation Results

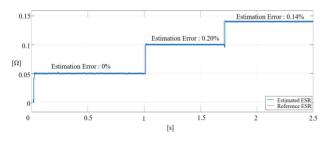

그림 5 DC-Link 커패시터의 ESR 추정 결과 Fig. 5 DC-Link Capacitor ESR Estimation Results

커패시턴스는 20% 감소되고 ESR은 2.8배 증가된다. 그림 4는 DC-Link 커패시터의 커패시턴스 추정 결과를 나타내고, 그림

5는 DC-Link 커패시터의 ESR 추정 결과를 나타낸다. 컨버터 제어에 따라 DC-Link 전압이 안정화된 후, 인버터의 제어기가 동작하여 시스템이 안정화되는 과도 구간 및 변동되는 파라미터가 하나의 주파수 분석 윈도우에 포함되는 구간을 제외하면커패시턴스 추정오차는 약 0.63% 이내, ESR의 추정 오차는 약 0.2% 이내로 나타난다. 각 구간의 오차는 과도 상태를 제외하고 구간 평균값 기준으로 계산되었으며, 특정 구간의 데이터를기반으로 하는 주파수 분석 기법의 특성상 커패시턴스 및 ESR값이 변동하는 구간에서는 추정 정확도가 떨어진다. 본 시뮬레이션에서는 커패시턴스 및 ESR을 Step으로 변경하기에 이러한한계가 더욱 두드러지게 나타났지만, 실제 환경에서는 커패시턴스 및 ESR의 변동이 점진적으로 나타나기에 이로 인한 영향을 미미할 것으로 기대된다.

### 3. 결 론

본 논문에서는 Two stage 인버터 시스템의 스위칭 주파수 차이로 인하여 생성되는 Beat 주파수 성분과 시스템의 6차 고조파 성분을 STFT를 통해 분석하여 DC-Link 커패시터의 커패시턴스 및 ESR을 추정한다. 커패시턴스 성분이 주로 나타나는 6차 고조파 주파수에서는 커패시턴스를, ESR 성분이 주로나타나는 Beat 주파수에서는 ESR을 추정하여 추정의 정확성을 높인다. 시뮬레이션 모델 검증을 통해 10kW급 3상 Two stage 인버터의 DC-link 커패시턴스와 ESR을 각각 약 0.63%이내, ESR의 추정 오차는 약 0.2%이내로 추정하였다.

제안된 추정 기법은 주파수 차이가 있는 신호들이 상호작용하는 시스템에서 효과적으로 활용될 수 있으며, 다양한 전력 전자 회로에도 확장 적용이 가능할 것으로 기대된다.

This research was funded by Korea Institute of Science and Technology (2E32971)  $\,$

#### 참 고 문 헌

- [1] M. K. P. M. Ramees and M. W. Ahmad, "Advances in Capacitor Health Monitoring Techniques for Power Converters: A Review," in *IEEE Access*, vol. 11, pp. 133540–133576, 2023.

- [2] Z. Zhao, P. Davari, W. Lu, H. Wang and F. Blaabjerg, "An Overview of Condition Monitoring Techniques for Capacitors in DC-Link Applications," in *IEEE Transactions on Power Electronics*, vol. 36, no. 4, pp. 3692–3716, April 2021.

- [3] Z. Zhao, P. Davari, W. Lu and F. Blaabjerg, "Online DC-Link Capacitance Monitoring for Digital-Controlled Boost PFC Converters Without Additional Sampling Devices," in *IEEE Transactions on Industrial Electronics*, vol. 70, no. 1, pp. 907–920, Jan. 2023.