# What are FOMs of SiC MOSFET

# - How important they are

Jaeeul Yeon Ph. D. 04 July. 2024

# **Goal of Presentation**

✓ Understanding FOMs of SiC MOSFET

✓ How they are used in practical

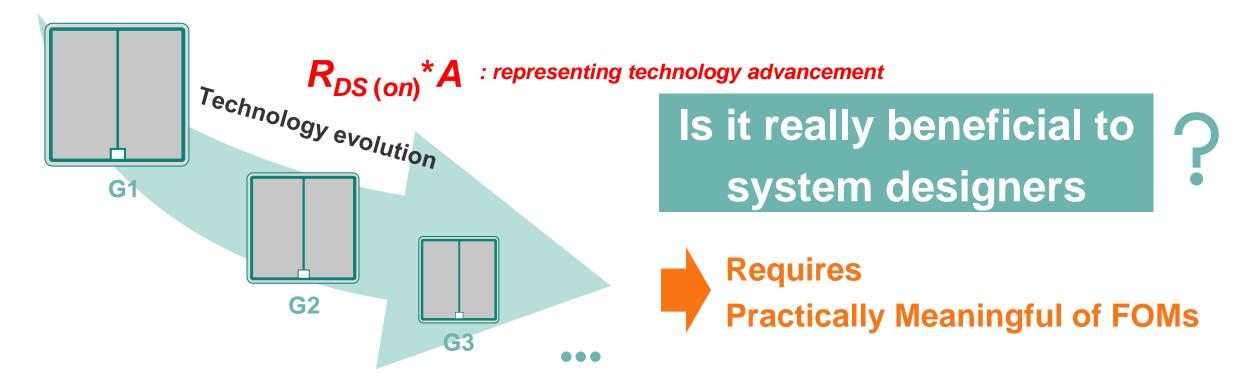

### FOM (figure of merit) of SiC MOSFETs

A numerical performance indicator of a device expressed by multiplied by R<sub>DS(on)</sub> and one or more parameters of device

- it will turn out to benefits

- ► The smaller the value, the better the performance

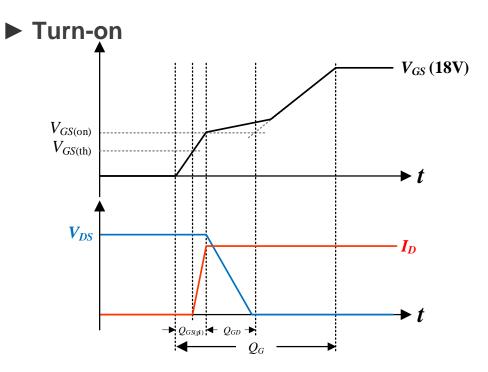

### Input capacitance related

## $R_{DS(on)}^*Q_{GD}$

- Product of the drain-source on resistance R<sub>DS(on)</sub> and the gate charge Q<sub>GD</sub>

- Can be good indicator to define from a conduction and switching performance perspective

#### Example; IMBG120R026M2H

| Parameter            | Symbol              | Note or test condition                                                            | Values |      |      | Unit |

|----------------------|---------------------|-----------------------------------------------------------------------------------|--------|------|------|------|

|                      |                     |                                                                                   | Min.   | Тур. | Max. | 1    |

| Total gate charge    | Q <sub>G</sub>      | $V_{\rm DD}$ = 800 V, $I_{\rm D}$ = 27.3 A, $V_{\rm GS}$ = -2/18 V, turn-on pulse |        | 60   |      | nC   |

| Plateau gate charge  | Q <sub>GS(pl)</sub> | $V_{\rm DD}$ = 800 V, $I_{\rm D}$ = 27.3 A, $V_{\rm GS}$ = -2/18 V, turn-on pulse |        | 12.9 |      | nC   |

| Gate-to-drain charge | Q <sub>GD</sub>     | $V_{\rm DD}$ = 800 V, $I_{\rm D}$ = 27.3 A, $V_{\rm GS}$ = -2/18 V, turn-on pulse |        | 16.2 |      | nC   |

### **Output capacitance related**

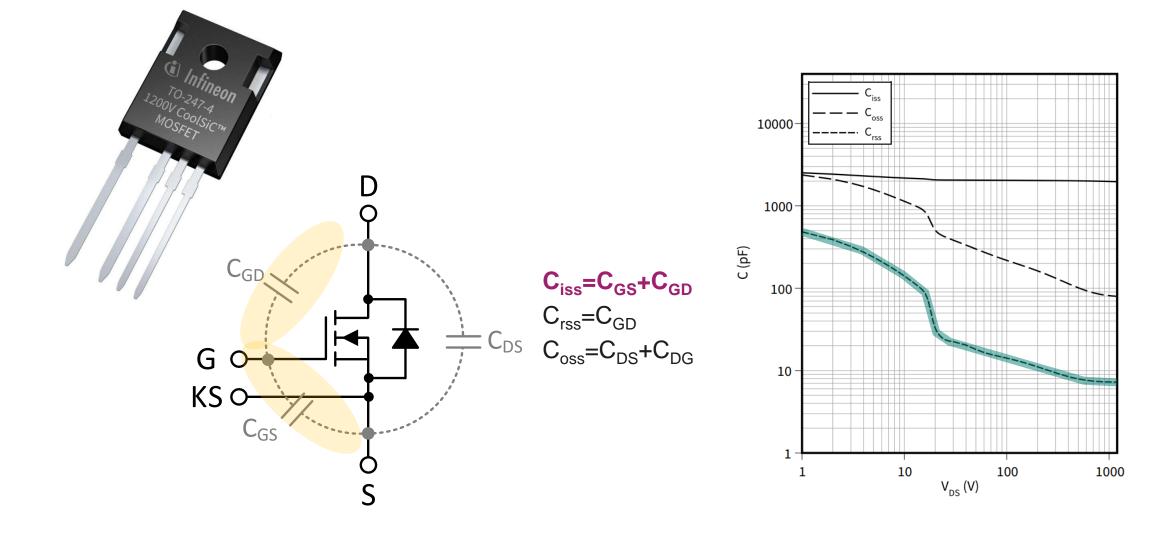

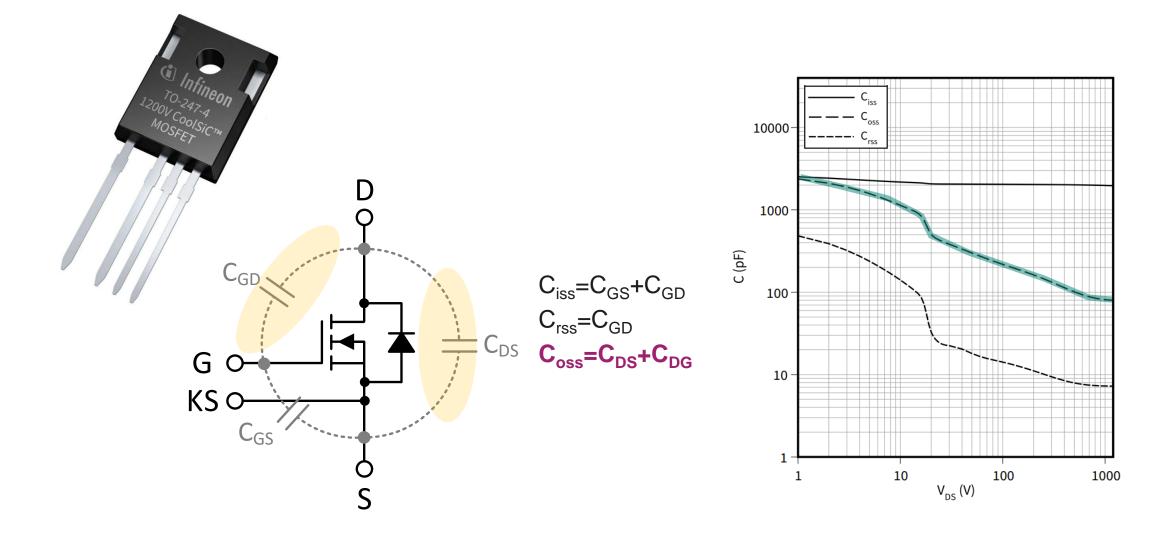

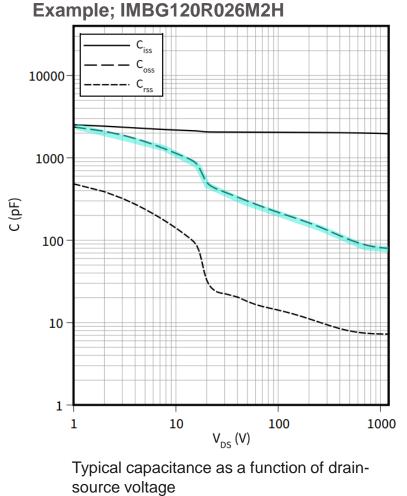

## **C**<sub>oss</sub> (output capacitance) of SiC MOSFET

C = f(VDS) f = 100 kHz, VGS = 0 V

Not stable and proportional to Drain-source voltage  $C_{oss}$ ,  $Q_{oss}$  and  $E_{oss}$  cannot correlate with each other unlike ordinary capacitor  $E_{oss V_{DS}} \neq C_{oss@V_{DS}} V_{DS}^2 \neq C_{oss} Q_{oss@V_{DS}}$ One of crucial device parameter affecting system performance Need to consider each for different applications (hard

switching or soft switching)

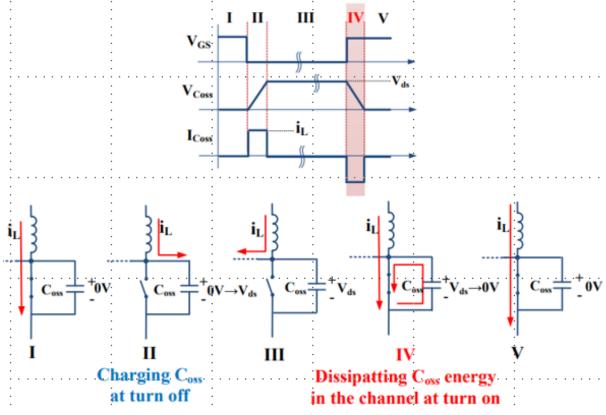

## R<sub>DS(on)</sub>\*E<sub>OSS</sub> or (R<sub>DS(on)</sub>\* C<sub>o(er)</sub>)- Hard-switching related

- Indicating the intrinsic turn-on energy loss

- The smaller E<sub>OSS</sub> value (in the equivalent R<sub>DS(on)</sub>), the less switching energy loss induced

- Regardless of the switching current

- Proportional to the switching frequency

- In the worst case, Tc(T<sub>vj</sub>) may significantly rise with no load condition at high switching frequency

$$E_{oss\_800V} = \int_0^{800} vC(v) dv = C_{o(er)} 800^2$$

- It needs integration to get hard for designer to know the value

- Infineon offers the value in datasheets from G2

#### Example; IMBG120R026M2H

| C <sub>oss</sub> stored energy                     | Eoss               | $V_{\rm DD}$ = 800 V, $V_{\rm GS}$ = 0 V, $f$ = 100 kHz, $V_{\rm AC}$ = 25 mV | 30  | 6   | μJ |

|----------------------------------------------------|--------------------|-------------------------------------------------------------------------------|-----|-----|----|

| Output charge                                      | Q <sub>oss</sub>   | Calculated by $C_{oss}(f)V_{DS}$ @100 kHz                                     | 132 | 2.6 | nC |

| Effective output<br>capacitance, energy<br>related | C <sub>o(er)</sub> | <i>V</i> <sub>DD</sub> = 0800 V, <i>V</i> <sub>GS</sub> = 0 V                 | 112 | 2.5 | pF |

| Effective output<br>capacitance, time related      | C <sub>o(tr)</sub> | $I_{C} = \text{constant}, V_{DD} = 0800 \text{ V}, V_{GS} = 0 \text{ V}$      | 165 | 5.7 | pF |

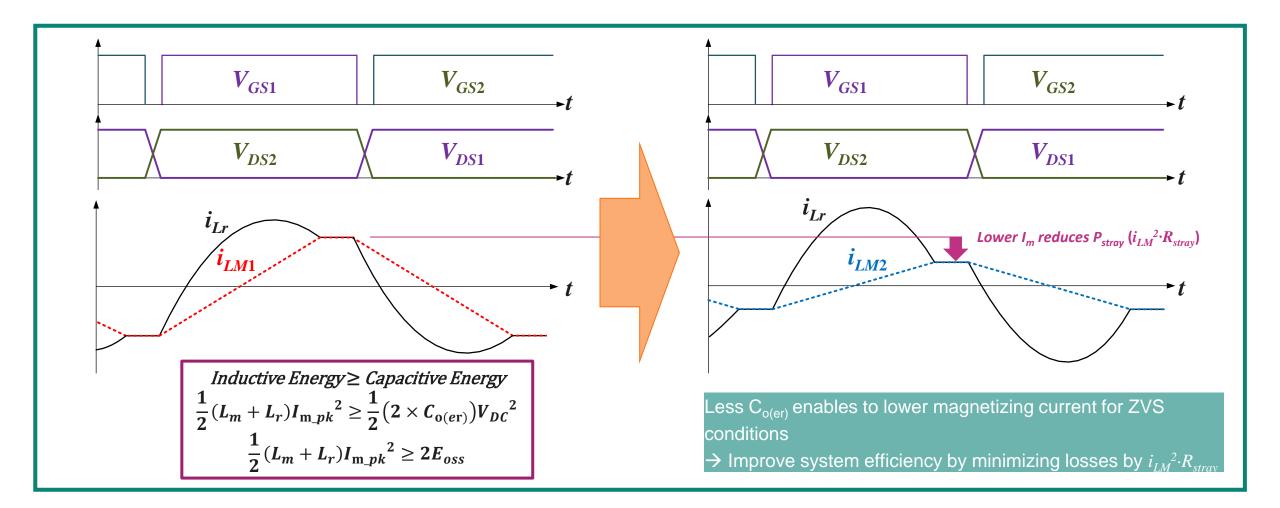

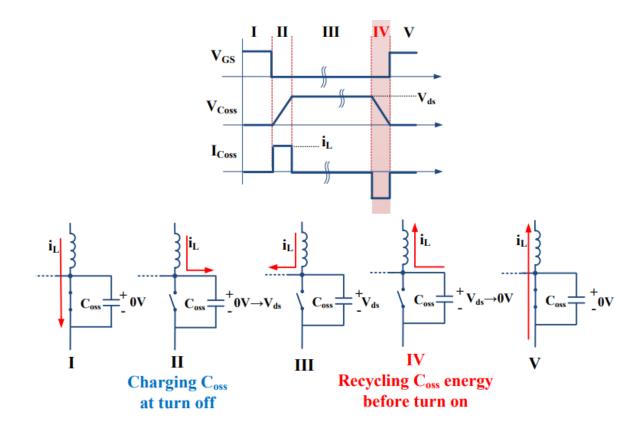

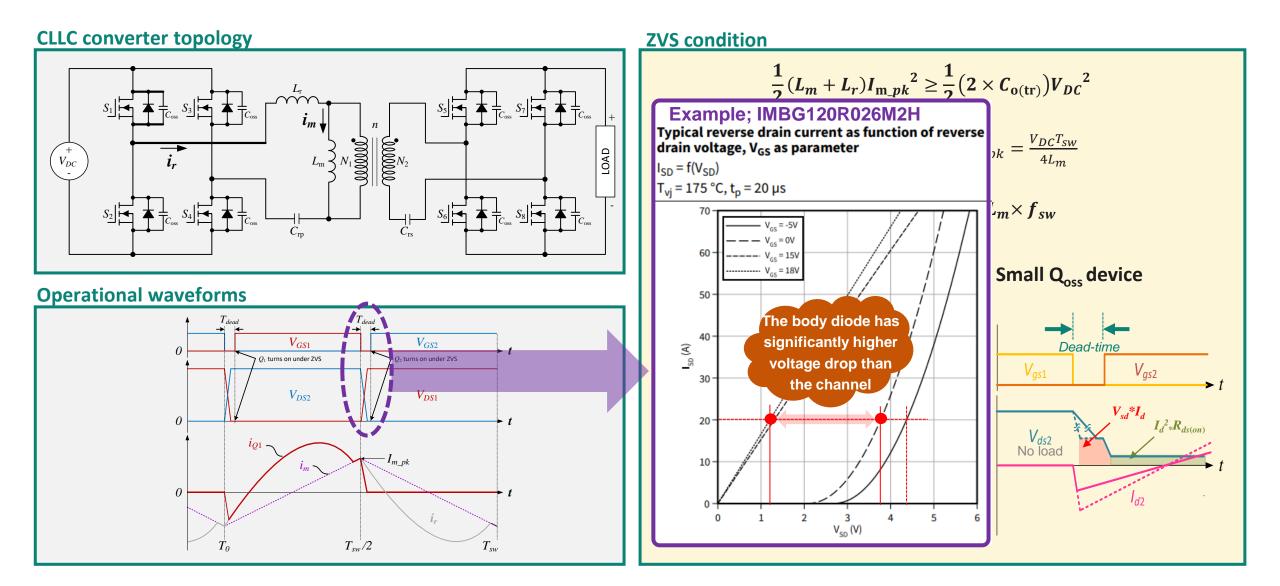

# $R_{DS(on)} * E_{OSS}$ or $R_{DS(on)} * C_{o(er)}$ - Soft-switching related

- LLC converter topology

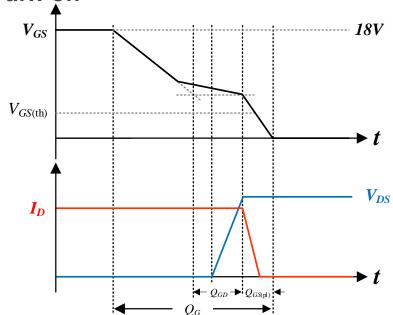

## $R_{DS(on)}^{*}Q_{OSS}$ or ( $R_{DS(on)}^{*}C_{o(tr)}$ ) - Soft-switching related

- Determining the deadtime to form ZVS (zero voltage switching) turn-on

- The smaller Q<sub>OSS</sub> value (in the equivalent R<sub>DS(on)</sub>) the less the deadtime

- Minimizes the body diode conduction time

- Enables higher switching frequency

$$Q_{oss_{800V}} = \int_{0}^{800} C(v) dv = C_{o(tr)} \times 800$$

- It needs integration to get hard for designer to know the value

- Infineon offers the value in datasheets from G2

#### Example; IMBG120R026M2H

| C <sub>oss</sub> stored energy                     | E <sub>oss</sub>   | $V_{\rm DD}$ = 800 V, $V_{\rm GS}$ = 0 V, $f$ = 100 kHz, $V_{\rm AC}$ = 25 mV | 36    | μJ |

|----------------------------------------------------|--------------------|-------------------------------------------------------------------------------|-------|----|

| Output charge                                      | Q <sub>oss</sub>   | Calculated by C <sub>oss</sub> (f)V <sub>DS</sub> @100 kHz                    | 132.6 | nC |

| Effective output<br>capacitance, energy<br>related | C <sub>o(er)</sub> | V <sub>DD</sub> = 0800 V, V <sub>GS</sub> = 0 V                               | 112.5 | рF |

| Effective output<br>capacitance, time related      | C <sub>o(tr)</sub> | $I_{\rm C}$ = constant, $V_{\rm DD}$ = 0800 V, $V_{\rm GS}$ = 0 V             | 165.7 | pF |

### Where is Q<sub>oss</sub>, C<sub>o(tr)</sub> considered

- Determining Dead-time LLC converter topology

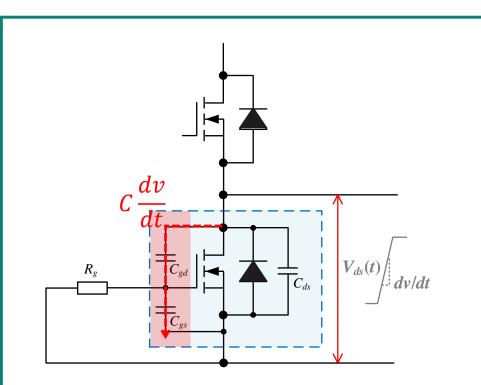

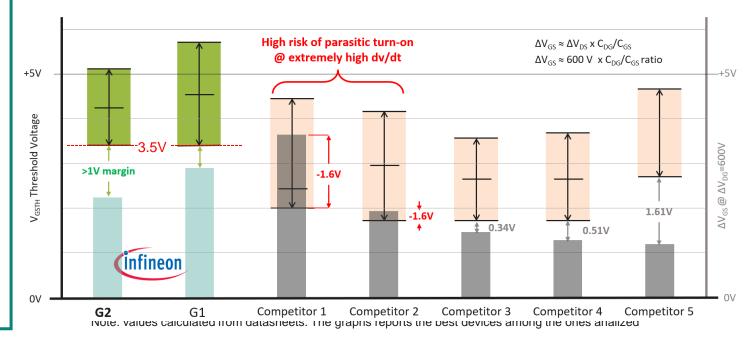

## PTO (parasitic turn on) immunity: 1/V<sub>GS(th)</sub>\*Q<sub>gd</sub>/Q<sub>gs</sub>

- PTO(parasitic turn on ) event occurs when extreme dv/dt applies to the SiC MOSFET

- PTO increases the turn-on losses significantly and eventually can be potential device failure

$1/V_{GS(th)}^*Q_{gd}/Q_{gs}$  is the FOM for determining the device safety from PTO

- The lower the 1/V<sub>GS(th)</sub>\*Q<sub>gd</sub>/Q<sub>gs</sub> factor is, the less likely to have parasitic turn on

- $\rightarrow$  Enables to allow unipolar drive (0 V gate voltage turn off)

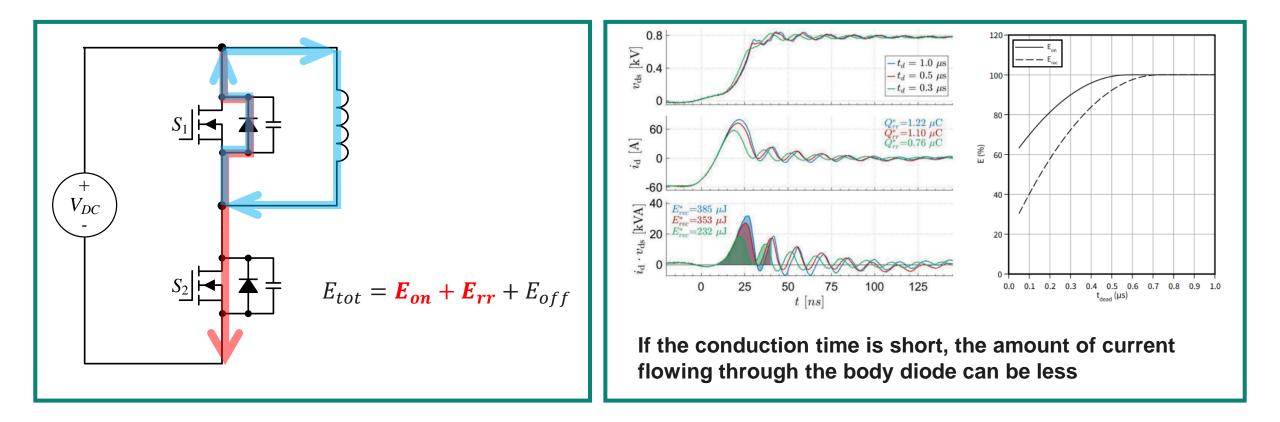

### Effect of Deadtime on Switching Loss of SiC MOSFET

- > In the SiC MOSFET bridge structure, the longer the deadtime the greater the switching loss

- o SiC PN diode takes longer time to complete equilibrium than Si diode

- Initial voltage barrier is high and it gradually decreases

### Summary

R<sub>DS(on)</sub>\*Q<sub>GD</sub> indicates switching performance with equivalent R<sub>DS(on)</sub>

#### R<sub>DS(on)</sub>\*E<sub>OSS</sub> indicates intrinsic power dissipation with equivalent R<sub>DS(on)</sub>

- Related to hard switching applications

- irreverent switching current

- Proportional to f<sub>sw</sub>

- R<sub>DS(on)</sub>\*Q<sub>OSS</sub> or (R<sub>DS(on)</sub>\* C<sub>o(tr)</sub>) indicates intrinsic power dissipation with equivalent R<sub>DS(on)</sub>

- Related to soft switching applications

- Affects to the deadtime for ZVS

**Optimized deadtime with SiC MSOFET enhances system efficiency significantly**

# Q&A